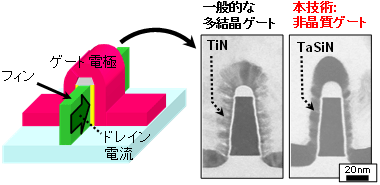

左は、フィンFETの模式図。右は、非晶質金属ゲートと多結晶金属ゲート電極の断面電子顕微鏡写真(提供:(独)産業技術総合研究所)

(独)産業技術総合研究所は12月15日、アナログ集積回路の小型化の妨げになっている低周波ノイズを劇的に低減した立体型トランジスタを開発したと発表した。スマートフォンやタブレットなどの高性能な無線端末の低コスト化や、現状よりも高い周波数動作が必要な次世代高速無線通信の普及促進が期待できるという。

■従来比5分の1に低減

アナログ回路はスマートフォンやタブレット端末をはじめ民生用ビデオ、オーディオ製品、パソコン周辺機器などにデジタル回路とともに組み込まれ、幅広く使用されている。

しかし、アナログ回路はトランジスタを微細にすればするほど増加する低周波ノイズの問題を抱えている。ノイズの影響を受けないデジタル回路の微細化が大きく進展しているのに対して、アナログ回路はその進行が遅れ、チップ面積縮小や高性能化の妨げになっている。

今回産総研のチームがノイズ低減を実現した立体型トランジスタは、フィンFETと呼ばれるトランジスタ。シリコン基板上に立体的に起立したチャンネルを持ち、その形が魚のひれ(フィン)に似ていることからフィンFETと呼ばれている。

研究チームは特性のバラツキを抑えるのに有効な非晶質金属ゲートをフィンFETに導入し、通常の多結晶金属ゲート電極を用いる場合に比べ、低周波ノイズを従来比5分の1に減らすことに成功した。

ゲート電極に多結晶金属を用いた場合と非晶質金属を用いた場合のノイズ波形を比べたところ、多結晶金属ゲート電極ではノイズが顕著に観測されたが、非晶質金属ゲート電極ではノイズの振幅が非常に小さく抑えられていた。

このようなノイズ抑制効果が得られると、アナログ集積回路のチップ面積を5分の1にまで縮小してもノイズ増加を引き起こすことがなく、集積回路のコスト低減のメリットを引き出すことが期待できるという。

アナログ集積回路の小型化、高性能化を可能にする成果で、スマートフォンなどの低コスト化、高性能化への波及は大きいとしている。