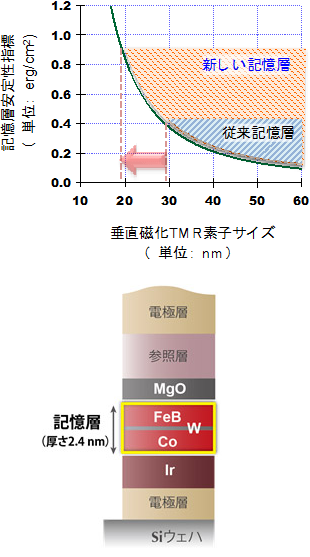

上は、記憶層の安定性と作製可能な垂直磁化TMR素子サイズの相関図。今回開発した新しい記憶層では、記憶層安定性指標を従来比2倍に強めたことで19nmサイズを可能にした。下は、今回開発した垂直磁化TMR素子の断面構造模式図(提供:(国)産業技術総合研究所)

(国)産業技術総合研究所・スピントロニクス研究センターは12月17日、次世代の大型記憶素子の心臓部に使われる垂直磁化トンネル磁気抵抗(TMR)素子の記憶安定性を、従来の2倍に向上させたと発表した。記憶層の一部にイリジウム層と極薄のコバルト薄膜を導入した。電源を切っても記憶内容を保持できて、高速での書き換えがほぼ無制限にできるため、省エネ型の理想的なメモリーとしての期待が大きい。従来の半導体メモリー(DRAM)に取って代わる新たな素子で、モバイル(携帯)電子機器などへの実用化も近いとみられる。

■大容量メモリーの実用化開発を加速

ベースとなるTMR素子は、2種類の強磁性体(金属)の間に絶縁体をサンドイッチ状に挟み、それぞれが数nm(ナノメートル、 1nmは10億分の1m)以下の極薄層でできている。磁場のかけ方によって、絶縁体層にトンネル電流の流れ方が変わり、電気抵抗が高抵抗状態と低抵抗状態に変わるため、それぞれを信号の1と0に対応させて情報を記憶させる。TMR素子は最新のハードディスクやビデオテープなどの記録メディアに使われるようになり、情報の読み出し用として実用化されている。

このTMR素子を組み込んだスピントルク書込型磁気ランダムアクセスメモリー(STT-MRAM)は、次世代の大型記憶素子として有望視されている。しかし素子サイズを小さくするほど記憶安定性が難しくなり、30nm以下のTMR開発が難航していた。

イリジウム層とコバルト層を接触させると両者が混じり合う問題などがあったが、産総研は独自の成膜技術を使って、混じりを原子レベルで防止することに成功した。

垂直磁化TMR素子は、イリジウム薄膜とコバルト薄膜の上に積層した。記憶層はコバルト、タングステン、鉄・ホウ素の3層一体で構成されている。コバルト薄膜と極薄タングステン薄膜の界面を作ることで、記憶層の体積を変えることなく記憶安定性を2倍に向上させることができた。

これによって19nmサイズのSTT-MRAMの条件がそろった。大容量メモリーの量産化にも拍車がかかるとみられている。