|

(独)産業技術総合研究所は12月12日、“次世代のトランジスタ”として世界中で開発競争が展開されている「フィンFET(フィン型電界効果トランジスタ)」で特性のバラつきが世界最小の素子を作ることに成功したと発表した。

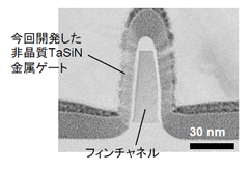

フィンFETは、超微細な電極を魚のヒレ(フィン)のように突起させた立体型半導体素子。現在の半導体素子は、平面でできているが、2017年以降に市場投入が想定されている素子の最小線幅は14nm(ナノメートル、1nmは10億分の1m)にまで微細化し、平面型から立体型のフィンFETの時代を迎えるとみられている。

しかし、フィンFETは、フィンに金属製の電極(ゲート電極)を使うため「しきい値(ち)電圧」(電流が流れ始める最小の電圧)がバラついてしまう大きな問題を抱えている。金属は、多結晶体なので結晶粒界でバラつきが発生してしまうからだ。

産総研は、フィンFETのゲート電極に結晶粒界を持たない非晶質金属材料の「窒化タンタルシリコン(TaSiN)」を使い、しきい値のバラつき強度を従来のゲート電極材料の多結晶金属(窒化チタン)の約半分にあたる世界最小値にまで小さくすることに成功した。

この研究開発は、(独)新エネルギー・産業技術総合開発機構の委託事業「ナノエレクトロニクス半導体新材料・新構造ナノ電子デバイス技術開発」の一環で行なわれた。

産総研は、この技術がトランジスタの微細化に伴うしきい値のバラつきを抑制するブレークスルーになるとみており、今後デバイスメーカー、半導体製造装置メーカー、材料メーカー、計測評価機器メーカーなどへの技術移転を推進していくことにしている。

詳しくはこちら

|

|

| 新開発の非晶質窒化タンタルシリコン製金属ゲートの拡大断面写真(提供:産業技術総合研究所) |

|