(独)産業技術総合研究所とシャープ(株)、(株)アルバック、金沢大学は5月18日、次世代の不揮発性メモリーと期待されている「抵抗変化メモリー(RRAM)」素子を128K(キロ)ビットのメモリーチップに集積化するプロセスを開発し、8インチ(1インチは2.54cm)ウエハー上に作ることに成功したと発表した。

RRAMは、遷移金属酸化物を金属電極で挟んだ構造の記憶素子(メモリー)で、酸化膜の電気抵抗変化を情報として記憶する。低消費電力で高速動作する長所を兼ね備えていることから、次世代のメモリーとして早期の実用化が待たれている。

同研究所は、2008年に超低消費電力と高速書き換え性能を併せ持ったRRAM素子の開発に成功。今回、その実用化に向け、集積化回路とメモリーアレイをウエハーレベルで作るプロセス開発と、その信頼性評価の基盤構築に挑んだ。

シャープとアルバックは、産総研が2008年に開発したRRAMの素子構造を8インチウエハーの上に作る信頼性の高い製膜・加工プロセス技術の開発を担当した。

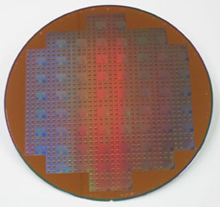

128Kビットメモリーチップは、約5mm角大で、8インチウエハー上のRRAMチップの数は約100個。ウエハー上にメモリーアレイを作製する際に重要な酸化物薄膜の厚さの均一性は、成膜時に使う酸素ガス量のコントロールで達成した。金沢大学が設計したメモリーアレイ評価用回路によってメモリーアレイの信頼性評価もできる。

試作したRRAM素子の材料には、現在のCMOS(相補型金属酸化膜半導体)プロセスに馴染み易いものを用いており、電極なども高価な材料を使っていない。このため、現在の半導体技術でウエハー上にチップを集積でき、生産コストを抑えることができるという。

詳しくはこちら |  |

| 8インチウエハー上に作製した128KビットRRAMチップアレイ(提供:産業技術総合研究所) |

|