(独)産業技術総合研究所は6月15日、2013年頃に実用化が見込まれる次の22nm(ナノメートル、1nmは10億分の1m)世代LSI(大規模集積回路)開発に向けて「フィンFET(フィン型マルチゲート電界効果型トランジスタ)」と呼ばれる立体型トランジスタの試作に成功したと発表した。CMOS(相補型金属酸化膜半導体)の材料や作製プロセスなどの改善により素子特性(しきい値電圧)のバラツキが大幅に減少、22nm世代LSI作りでの歩留まり向上が期待される。

これまで、シリコンLSIの高性能・高集積化は、最小構成単位のトランジスタの微細化で進んできたが、次の22nm世代ではその寸法の小ささから来る素子間の特性のバラツキによる製品の歩留まり低下が心配される。

同研究所は、特性のバラツキ低減を目指して22nm世代のフィンFET作りの作製プロセスを新たに開発、その手法を用いてトランジスタを試作した。

まず、チャネルと呼ばれる部分の材料に不純物無添加の純シリコンを採用、不純物によるバラツキを完全に除去した。また、シリコンの結晶面によってエッチング速度が異なるエッチング(高異方性ウエットエッチング)を導入、チャネルの側壁が原子レベルで平坦に形成できるようになった。これでチャネルの厚さのバラツキが抑えられるばかりでなく、チャネル側壁面に凹凸が生じないため、この壁の上に堆積されるゲート金属も厚さ一様に堆積され、金属ゲートから電子を取り出す最小エネルギー(仕事関数)のバラツキも極限まで低減できた。

システムLSIやCMOSでは、SRAM(記憶保持動作不要の随時書き込み読み出しメモリー)で最小寸法のトランジスタを多用することから、特性バラツキの影響を受けやすい。同研究所は、今後、このフィンFETでSRAMを実際に作製し、歩留まり向上の実証を行う。 詳しくはこちら |  |

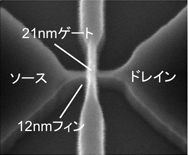

| 試作した新トランジスタの構造(提供:産業技術総合研究所) |

|