(国)産業技術総合研究所は7月1日、ディスプレーの表示素子を制御する数百万個の有機トランジスタから成る駆動回路パネルを非破壊で一括検査できる技術を開発したと発表した。大面積のパネルの素子性能を短時間で検査できるため、印刷手法による大規模なデバイス製造に道が開けるという。

■印刷手法利用の大規模なデバイス製造に道

液晶ディスプレーなどの表示素子を制御する駆動回路パネルはアクティブバックプレーンと呼ばれ、大面積化が進んでいる。近い将来は印刷手法を利用したプリンテッドエレクトロニクス技術により、数百万個以上の有機トランジスタから成るデバイス製造が考えられている。

しかし、現行の素子検査法では検査に時間がかかり過ぎるなどの問題があり、印刷法を用いたアクティブバックプレーンの製造技術の開発と並んで、それに対応できる高速なデバイス性能評価技術の開発が課題になっていた。

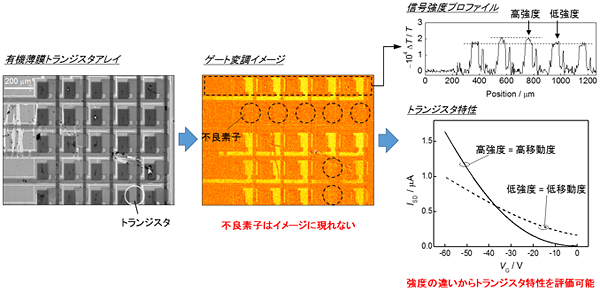

研究グループは今回、デバイス性能の分布を光学イメージ化する「ゲート変調イメージング法」という技術を開発した。

ゲート変調イメージング法は、有機トランジスタにゲート電圧をかけた時に生じる有機半導体層の光透過率・反射率の微小な変化を受光センサーで撮影、ゲート電圧をかけた状態とかけてない状態の差を画像処理して微小な変化イメージ(ゲート変調イメージ)を高感度で得るというもの。

ゲート変調イメージには、正常動作するトランジスタだけが現れるため、配線不良や半導体層の欠陥による動作不良個所を特定できる。アクティブバックプレーンを構成する膨大な数の有機トランジスタの性能分布を一括して評価でき、各素子の検査に要する時間を大幅に短縮できる。

研究グループは今後、このイメージング技術の高速・高感度化、検査範囲の大面積化を進め、実用化したいとしている。

有機トランジスタアレイのゲート変調イメージング測定結果(提供:(国)産業技術総合研究所)