(独)産業技術総合研究所は11月27日、(株)船井電機新応用技術研究所と共同で次世代のメモリー(記憶素子)として注目されている「ナノギャップメモリー」の新しい構造方式を開発、集積化に成功したと発表した。

ナノギャップメモリーは、10nm(ナノメートル、1nmは10億分の1m)ほどの間隔(ナノギャップ)で向かい合った2つの金属電極に電圧を加えると、ギャップ幅がトンネル抵抗の変化を反映して変わり、それに伴って抵抗が桁違いに変わることを利用した記憶素子のこと。高集積性と高速性の両立を目指す次世代の不揮発性メモリー(電源を切っても情報を保持できる記憶素子)の一つとして研究開発されている。

同研究所は、船井電機新応用技術研究所などと共に、この抵抗変化メモリーのメカニズムの解明、集積化デバイスの作成・評価などを行っているが、従来はメモリー部となるナノギャップが絶縁体基板上に平面配置されていたため、配線まで含む素子サイズが大きくなり、集積化には不向きだった。

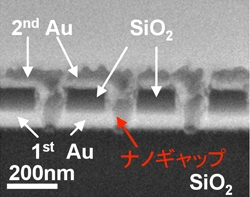

今回両者は、酸化シリコン層にエッチングで穴構造を作り、その壁面に縦方向にナノギャップを作り込む構造方式の開発に成功した(写真)。これだと配線の交差点に素子を置けるため、平面型より遙かに集積化し易い。

既にナノギャップが実際に穴の壁に出来て良好なメモリー動作することを確かめており、10ナノ秒(1ナノ秒は10億分の1秒)のパルス電圧での書き込み・消去可能な高速スイッチング動作、10万回以上の繰り返し動作、半年を超える記憶状態保持を確認済み。

この新構造方式のメモリーは、構造が単純で、既存プロセスとも整合性が良く、電極には各種の金属・合金など幅広い材料が使えるので、超高密度不揮発性メモリーの実現が期待される。

詳しくはこちら |  |

| 新開発の縦型ナノギャップメモリーの拡大断面写真。Auは金、SiO2は酸化シリコン(提供:産業技術総合研究所) |

|